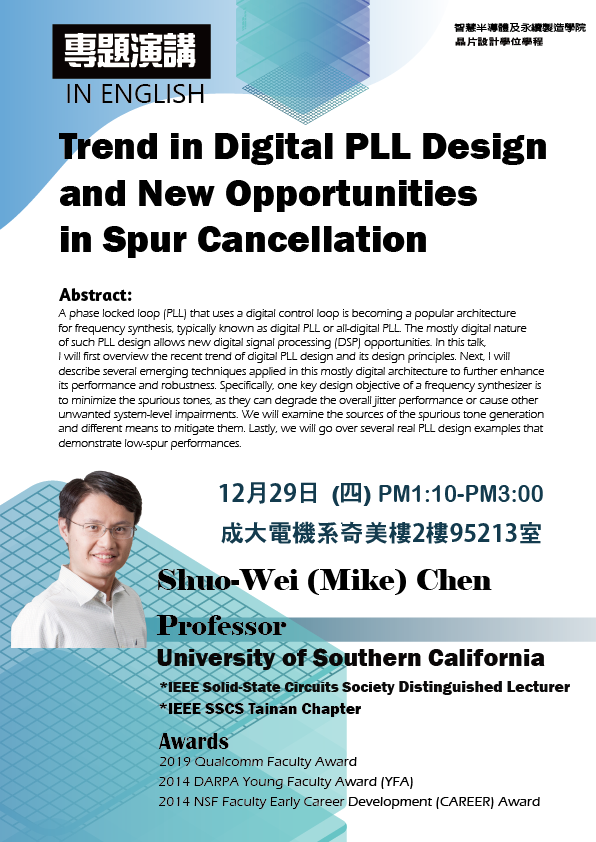

講者:Shuo-Wei (Mike) Chen

講者經歷:

University of Southern California Professor

IEEE Solid-State Circuits Society Distinguished Lecture

IEEE SSCS Tainan Chapter

講題:Trend in Digital PLL Design and New Opportunities in Spur Cancellation( in English)

時間:111年12月29日(四)下午1點10分

地點:電機系奇美樓2樓95213室

演講摘要:

A phase locked loop (PLL) that uses a digital control loop is becoming a popular architecture

for frequency synthesis, typically known as digital PLL or all-digital PLL. The mostly digital nature

of such PLL design allows new digital signal processing (DSP) opportunities. In this talk,

I will first overview the recent trend of digital PLL design and its design principles. Next, I will

describe several emerging techniques applied in this mostly digital architecture to further enhance

its performance and robustness. Specifically, one key design objective of a frequency synthesizer is

to minimize the spurious tones, as they can degrade the overall jitter performance or cause other

unwanted system-level impairments. We will examine the sources of the spurious tone generation

and different means to mitigate them. Lastly, we will go over several real PLL design examples that

demonstrate low-spur performances.

瀏覽數:1163

公告類型: 公告/一般

公告狀態: 一般

公告人員: 網頁助教 Pao

公告日期: 2022 / 12 / 04 11:44

更新日期: 2022 / 12 / 04 11:44